图像采集卡技术特点与指标

●视频输入标准视频信号和逐行非标准黑白视频信号。

●多路视频输入软件切换,可采集单场/单帧/连续帧。

●采集分辨率为768*576,1024*1024;

●最大点频170M;

●支持硬件任意开窗,二级缩放,硬件翻转

●有类似内存映射的功能,多个应用程序/进程可以共享其采集的图像数据;

●信号接入丢失感知,无信号不蓝屏、死机

●硬件控制帧率流量,可在实际使用中和其它采集卡配合,更有效提高PCI带宽的利用

●支持RGB32、RGB24、YUV422、RGB8等采集格式

●编程完全使用微软提供DirectShow/VFW接口,也可提供基于VC、VB、Delphi等演示程序和源代码。

●行场频全自动检测:具有全自动行场频自适应能力和信号自检测能力,信号源信号变化不需用户调节,完全适合无人值守应用

●可外触发(低电平沿)硬件采集控制,具有高带宽输入,数字抗混迭滤波技术。

图像采集卡原理

采集,视频/图象经过采样、量化以后转换为数字图象并输入、存储到帧存储器的过程。由于图像信号的传输需要很高的传输速度,通用的传输接口不能满足要求,因此需要图像采集卡。

从视频源得到的信号,经过视频接口送到视频采集卡,信号首先进过模数转换,然后送到数字解码器解码。模数转换器ADC实际上也是一个视频解码器,可以看出它对来自视频源的视频信号解码和数字化,另外,采用不同的颜色空间可选择不同的视频输入解码器芯片。

视频采集就是将视频源的模拟信号通过处理转变成数码信息,并将这些数码信息存储在电脑硬盘上的过程。这种模拟数码转变是通过视频采集卡上的采集芯片进行的。通常在采集过程,对数码信息还进行一定形式的实时压缩处理。

1、视野(FOV)或现场是相机及光学系统“看”到的真实世界的具体部分。

2、CCD芯片将光能转化为电能。

3、相机将此信息以模拟信号的格式输出至图像采集卡。

4、AD – 转换器将模拟信号转换成 8 位(或多位)的数字信号。每个象素独立地把光强以灰度值(Gray level)的形式表达。

5、这些光强值从CCD芯片的矩阵中被存储在内存的矩阵数据结构中。

灰度值(Gray Level)—— 象素光强弱信息的表示灰度值为真实世界图像量化的表现方法。通常灰度值从最黑到最白为0 - 255。光线进入CCD象素,如果光强达到CCD感应的极限,此象素为纯白色。对应于内存中该象素灰度值为255。如果完全没有光线进入CCD象素,此象素为纯黑色。对应于内存中该象素灰度值为0。

文章链接:中国安防展览网 http://www.afzhan.com/Tech[_]news/Detail/20924.html

选购图像采集卡的策略

许多数码达人对图像采集卡这个词并不陌生,众所周知,图像采集卡充当着链接摄像机与计算机的桥梁,将采集到的信息输送给电脑。那么摄像作为必不可少的部分,选购图像采集卡时要注意哪些方面呢?

下面为您简单介绍图像采集卡的技术参数以供参考。

图像采集卡的技术参数主要有以下几方面:

(1)图像传输格式

图像采集卡需要支持系统中摄像机所采用的输出信号格式。大多数摄像机采用RS422或EIA*(LVDS)作为输出信号格式。在数字相机中,IEEE1394,USB2.0和Camera Link几种图像传输形式则得到了广泛应用。

(2)图像格式(像素格式)

黑白图像:通常情况下,图像灰度等级可分为256级,即以8位表示。在对图像灰度有更精确要求时,可用10位、12位等来表示。

彩色图像:彩色图像可由RGB(YUV)3种色彩组合而成,根据其亮度级别的不同有8-8-8,10-10-10等格式。

(3)传输通道数

当摄像机以较高速率拍摄高分辨率的图像时,会产生很高的输出速率,这一般需要多路信号同时输出,因此好的图像采集卡要能支持多路输入。

一般情况下,图像采集卡有1路,2路,4路,8路输入等之分。

(4)分辨率

采集卡能支持的最大点阵反映了其分辨率的性能。一般采集卡可支持768*576点阵,而性能优异的采集卡,如维视数字图像技术有限公司生产的MV2000高清黑白图像采集卡,其支持的最大点阵可达2048*1536,很大程度上提高了成像质量。除此之外,单行最大点数和单帧最大行数也可反映采集卡的分辨率性能。

(5)采样频率

采样频率反映了采集卡处理图像的速度和能力。在进行高度图像采集时,需要注意采集卡的采样频率是否满足要求。目前高档采集卡的采样频率可达65MHZ。

(6) 传输速率

主流图像采集卡与主板间都采用PCI接口,其理论传输速度为132MB/S。

综上所述,想必您对图像采集卡这一概念有了初步的认识,希望可以对想要采购图像采集卡的达人们,提供一定帮助。

基于FPGA的图像采集卡的设计

1 引言

现代化生产和科学研究对视频图像采集系统的要求日益提高。传统的图像采集卡速度慢、处理功能简单、采用分立元件、电路非常复杂;而且可靠性差、不易调试、不能很好地满足特殊要求。FPGA(现场可编程门阵列)是专用集成电路中集成度最高的一种,用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户所需逻辑功能。用户对FPGA的编程数据放入芯片,通过上电加载到FPGA中,对其进行初始化;也可在线对其编程,实现系统在线重构。 基于FPGA技术的图像采集主要是通过集成的FPGA开发板,使用软件编程把图像的采集控制程序写入FPGA开发板的芯片上,通过仿真技术来进行图像的采集处理分析。通过这种方式,便于及时地发现设计中的错误,从而有效地缩短研发时间。

2 系统的组成及基本原理

该图像采集系统主要由模拟视频信号解码模块,I2C控制接口模块,采样控制模块,SDRAM存储控制模块。

图1 图像采集卡系统框架图

SAA7113H芯片把从CCD采集来的模拟视频信号转化成Y U V =4 2 2格式的数字图像信号。这些信号在同步脉冲的作用下进入采集控制器。采样控制器在奇偶场控制信号下把图像信息存入SDRAM中。该系统可以实现由隔行扫描图像到逐行图像的转化及存储。

2.1 模拟视频信号解码

由于SAA7113H芯片具有I2C接口,该模块则通过I2C总线来配置SAA7113H初始化的信息。工作涉及SAA7113H的初始化字的配置、工作方式的配置;行同步开始和结束标志位、确定亮度、色度、饱和度的大小以及输出图像数据信号的格式。

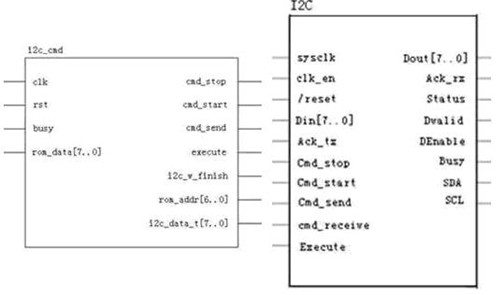

2.2 I2C控制接口模块

I2C模块作为SAA7113H寄存器初始配置的整体控制模块。具体可以分成I2C[_]cmd和数据传输两个模块。I2C[_]cmd模块为纯组合逻辑电路,完成信号的发送控制任务,配合rom[_]data[7.0]和rom[_]addr[7.0]信号完成数据的寻址与存入等工作;而数据传输模块主要和I2C[_]cmd模块一起组合成I2C的数据控制写入模块,它主要负责对I2C[_]cmd模块的输出信号进行缓存,并在其输出端输出I2C总线的串行数据SDA以及 I2C总线的串行时钟信号SCL。

图2 I2C控制模块及数据传输模块

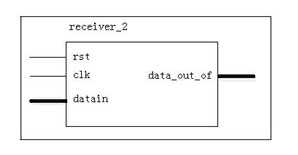

2.3采样控制模块

模块在Verilog编程语言的控制下,把SAA7113H输出的一帧灰度数字视频图像数据进行奇偶场的分开存储,达到隔行到逐行的图像转换,与此同时,通过控制行采集数和列采集数,满足720*576、25帧/秒的分辨率的要求。

图3采样控制器模块

2.4 SDRAM控制存储模块

图4 SDRAM控制及SDRAM存储模块

SDRAM模块作为数据的存储模块,可以具体分成SDRAM控制接口模块以及SDRAM存储模块(SDRAM)。SDRAM控制接口模块用于对数据存储的控制,发出控制读写信号来使数据存储到SDRAM模块里面;SDRAM模块则通过本身的逻辑存储单元,把从SDRAM控制接口模块出来的数据存储到自身的存储空间中。

3 方案模拟仿真及具体实现

3.1 采样控制器的功能仿真

图5 控制器同步状态机

Idel:默认空闲状态(开始或复位状态)。此时如果收到数据8‘hff,进入State1,其它情况在本状态停留。

State1: 开始接收数据状态。此时收到数据8’h00 ,进入State2;收到数据8’hff,停留在本状态,其它情况返回Idel。

State2:数据确认成功状态。此时若收到数据8’h00 ,数据确认成功,接下来输出图像视频信号,进入State3,其它情况状态转到Idel。

State3:视频图像数据的接收状态,表明数据采集及传送即将开始。在此状态下,若收到数据8’hc7,进入图像奇数场采集;若收到数据8’h80,进入图像偶数场采集。其它情况回到Idel。

State4:奇场图像采集状态。奇数场开始采集,同时输出场同步及奇场信号来控制计数器计数。与此同时,状态自动恢复到Idel。为下一次的图像场的采集做好准备。

State5:偶场图像采集状态。偶数场开始采集,同时输出场同步及偶场控制信号来控制计数器计数。与此同时,状态将自动恢复到Idel。为下一次的图像场采集做好准备。

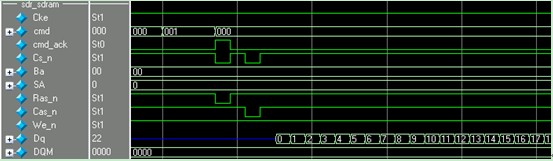

3.2 SDRAM控制存储模块仿真实现

1)数据的突发式读取

SDRAM支持的实突发式的读取。本文所设置的读取设为整页式突发读取,具体的工作过程:cmd发出001b的控制信号,进行带自动预充电的SDRAM读操作,cmd[_]ack发出高电平应答信号,同时Cs[_]n低电平表示片选有效。控制信号Ras[_]n、Cas[_]n、We[_]n的值输出为010b,表示进行带自动预充电的SDRAM操作,紧接着进行读操作。数据在读取的时候,从CAS读取指令发出到第一笔数据输出,存在读取潜伏期(CL)。故数据的读出有一定的时钟延迟,在本文中CL=2。即延时两个时钟周期,之后数据从Dq口从SDRAM读出。如图6所示是采用序列数读入时的modelsim的仿真图。

图6 数据的突发式读取时序图

2)数据的突发式写入

数据的整页式突发写过程与读操作类似:cmd控制信号010b控制进行带自动预充电的SDRAM写操作,cmd[_]ack应答,Cs[_]n低电平表示芯片选中工作。与此同时,控制信号Ras[_]n、Cas[_]n、We[_]n的值输出为011b,对行地址和列地址进行激活,然后发出100b写控制信号。由于信号的写入不需要时钟延迟,故此时数据从DATAIN口输入,经过寄存后从Dq存入SDRAM芯片里面,从而完成采集数据的存储。如图7所示是采用序列数写入时的modelsim的仿真图。

图7 数据的突发式写入时序图

4 结束语

该图像采集卡系统是基于FPGA技术,软件上则采用verilogHDL实现。此图像采集卡完全适用于静态图像以及帧数不是很多的动态图像。经过逻辑分析仪中的采集分析得知,对于一般25帧/秒的图像采集要求,该图像采集系统具有很好的效果。

本文是采用FPGA的图像采集技术,通过构造采样控器来实现图像信号隔行到逐行的转换,这样就避免了同时使用两个RAM来分别存储奇场信号和偶场信号。另外,与传统的RAM存储器相比,SDRAM存储器具有更高的读写速度。