# 基于 FPGA 的 LED 显示控制系统设计

## 张志伟 赵 峰

(陕西理工学院物理与电信工程学院, 汉中 723000)

摘 要 LED产业是21世纪最具有发展前景的高新技术产业。根据 LED 显示模块结构特点,应用 FPGA 技术对 LED 显示 屏的控制系统进行设计。显示控制系统由输入接口模块、信号写入控制模块、信号读取控制模块、读取控制模块、存储模块、 动态控制模块等模块构成。程序采用 Verilog-HDL 语言编写,从而实现外部输入信号的地址生成、选择、存储、动态控制等处理。实验测试结果表明:系统可以实现字符或图案的动态显示,具有实际应用价值。

关键词FPGALED控制系统Verilog设计中图法分类号TN873.5;文献标志码A

LED 显示屏是一种通过控制半导体发光二极管的亮度的方式,来显示文字、图形、图像、动画、行情、视频、录像信号等各种信息的显示屏幕。近几年来,作为半导体照明领域的一部分,城市景观照明及室内外装饰照明的霓虹灯和部分传统光源必将逐步被具有节能、环保、寿命长、可靠性高及可实现全彩变化的 LED 光源所取代。本设计使用 FPGA技术实现对 LED 显示系统的控制,采用自顶向下的设计方法,用模块调用实现任意字符和图案的动态显示[1,2]。

# 1 LED 显示模块工作原理

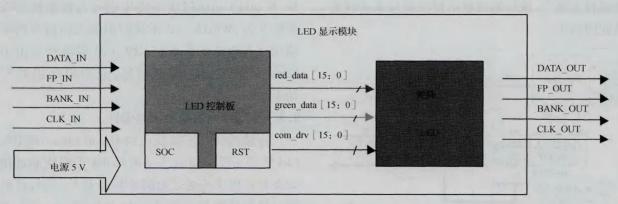

显示控制系统通过 RS232C 接口和外部 PC 进行数据交换,同时进行显示数据的传送和控制,最终实现对 LED 矩阵(256 点阵)的亮暗控制。本设计所用的 LED 显示模块结构如图 1 所示,此 LED 显示模块由矩阵 LED 和其控制部的 LED 控制板构成。LED 控制板的内部带有系统时钟(OSC),通过内部复位(RST)初始化。

图 1 LED 显示模块内部构成图

2012年9月6日收到

陕西省自然科学基础研究 (2011JO1003) 资助

第一作者简介:张志伟(1977一),男,湖南邵阳人,讲师,硕士。研究方向:电子技术和信号完整性分析。E-mail;zzw\_1997@163.com。

来自外部的输入信号为: CLK\_I.: 数据时钟信号(200kHz), FP\_I.: 帧脉冲信号,

BA. K\_I.: 面切换信号, DATA\_I.: 串行数据信号。数据为1个时钟传送1位, 即与数据时钟信号同步的串行数据。

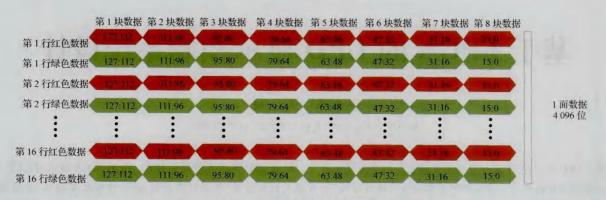

图 2 一面 LED 显示屏结构示意图

8 块 LED 显示模块构成显示屏,其结构示意图 如图 2 所示。矩阵 LED(16×16)1 行的数据为:256 位;1 面由 16 行构成。因此,1 面的数据为:1 面数据 = 256(位)×16(行)=4 096 位。数据以帧脉冲信号为基准,以帧为单位传送。1 帧数据 = 16(点)×8(块)=128 位,因此,传送 1 帧数据需要 128 时钟。

# 2 显示控制系统的设计

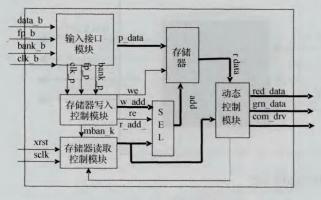

显示控制系统由输入接口模块、存储器写入控制模块、存储器读取控制模块、动态控制模块、SEL控制模块和存储器模块等六个子模块构成,其结构原理图如图3所示。设计采用Verilog HDL语言分模块编程实现<sup>[3]</sup>,最后通过顶层模块调用来实现整体功能的描述。

图 3 显示控制系统原理图

#### 2.1 输入接口模块设计

输入接口模块获取外部的串行数据(200 kHz) 信号,对其进行验证和判断后实现串行并行转换, 随后以16 位并行数据形式传输到输出接口模块、存 储器模块及存储器写入控制模块。

外部接收的数据信号、时钟信号、帧信号、面信号,在数据时钟的下降沿由 LATCH 子模块对输入信号进行锁存。锁存后的时钟信号、帧信号、面信号送入 SYNC 子模块,使其与系统时钟信号 selk 同步后,作为 elk\_p,fp\_p,bank\_p 信号传送到存储器写人控制模块。锁存信号 data\_l 在 S/P 子模块进行串行/并行变换,以 16 位并行数据信号 p\_data [15:0]传送至存储器模块,此时 p\_data [0]作为 s\_data 信号。

#### 2.2 存储器写入控制模块设计

存储器写入控制模块包括 3 个子模块,分别为W-add Count 模块、Wbank Ctrl 模块和 RW Ctrl 模块,W-add Count 模块主要生成写入数据的写入地址低 5 位,Wbank Ctrl 模块根据输入面信号的变化输出写入地址的低 6 位,RW Ctrl 模块接受由 Data Count 模块发出的控制信号,通知向存储器写入数据。

### 2.3 存储器读取控制模块设计

存储器读取控制模块由 R-add Count 和 RBank Ctrl 两个子模块构成, R-add Count 子模块通过接收动态显示模块传送过来的 led-clk 信号,进行计数工作。往返计数范围为 0—31,并生成读出地址低 5位 r-add[4:0]; RBank Ctrl 子模块通过接收来自存储器写入控制模块的面切换信号 m-bank 进行控制,生成存储器读取地址的最高位 r-add<sup>[5]</sup>。

## 2.4 SEL 模块设计

SEL 控制模块根据输入信号的读/写状态判断来传送地址信号, SEL 模块对存储器写入控制模块

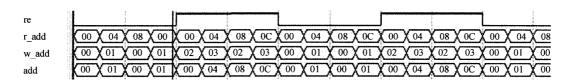

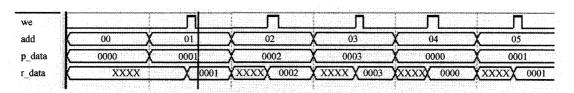

图 4 SEL 模块仿真时序图

的写入地址信号和存储器读取控制模块的读取地址 信号在 re 信号控制下进行选择性的输出,最后送入 存储器模块。

SEL 模块在读写控制端子的 re 的控制下,选取读出/写入信号。在 re 为 0 时把写地址 w\_add 的值赋给 add,当 re 为 1 时将 r\_add 的值赋给 add,实现读/写地址的选择。其 Quartues II 7.0 开发环境<sup>[4]</sup>下仿真时序图如图 4 所示:

#### 2.5 动态控制模块设计

动态控制模块由 LATCH-OUT、Drive Ctrl 及 TIM 三个子模块组成,LATCH-OUT 子模块提供 LED 显示的红绿灯信号,对存储模块的数据信号分别赋予红信号 red\_data 和绿信号 grn\_data,从而控制其图案和背景的颜色;Drive Ctrl 子模块是驱动 LED 进行显示,生成矩阵 LED 通用端子的控制信号和 LATCH 子模块的控制信号。当 led\_clk 为 1 时,读地址信号为 0或 1 时,让第一排灯亮,取 2 或 3 时第二排亮……30或 31 时第 16 排灯亮,从而实现动态显示;TIM 子模块则是一个计数模块,主要实现对 sclk 的分频控制,得到的 led\_clk 送入存储器读取控制模块,生成的频率范围一般在 600 Hz ~ 200 kHz,使汉字可以显示出来并看不出其在闪烁,同时还会参与读取地址信号的生成。实现 LED 的动态开灯控制的具体程序实现如下:

always@ (posedge sclk)//判断时钟信号 begin if(xrst = =0)

п(мы – – о

begin

red\_data < = 16 b000000000000000;//红灯信号初始状态 gm\_data < = 16 b0000000000000000;//绿灯信号初始状态 end

else if( $r_add = 0$ )

begin

grn\_data < = r\_data;//在地址信号最低位为 0 时,把字码信号赋给绿灯信号

red\_data < = 16 b11111111111111111;//在地址信号最低位为 0 时,红灯全灭

end

else

begin

red\_data < = r\_data;//在地址信号最低位为1时,把字码信号赋给红灯信号

gm\_data < = 16 b1111111111111111;//在地址信号最低位为 1 时,绿灯全灭

end

end

### 2.6 存储器模块设计

存储器模块针对在 SEL 模块被指定的地址,进行数据的写入与读出。由 we 信号控制,对输入接口模块的并行信号进行选择性的写入和读取,将读取的信号 r\_data 输出后送入动态控制模块。

初始时将存储器的地址[0001]和[0002]各自改写为[AAAA]和[BBBB]等数字,当存储器写入控制信号 we 为 L 时,读出数据为[AAAA]和[BBBB]。若we 变为 H,p\_data [15:0]的值被上传([1234]和[5678]),然后 we 变为 L 时,读出上传数据。存储器模块仿真时序图如图 5 所示。

图 5 存储器模块仿真时序图

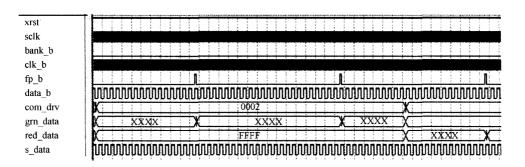

图 6 整体模块仿真时序图

## 3 结论

FPGA 技术的引入使得开发周期大大缩短,系统通用性和扩展性能大大提高<sup>[5]</sup>,显示控制系统的各子模块程序编译综合后通过总模块程序调用实现整体功能(由于篇幅原因具体总模块程序不在此罗列)。其仿真时序图如图 6 所示,通过波形可以得出其功能正常。

仿真成功后对总程序的各个输入输出脚进行管脚配置,通过 RS232 接口下载到 Altera 公司的可编程逻辑器件 EPF10K10TC 芯片,电路板的系统时钟用 10Mhz 的晶振。通过实验验证,用户可以根据需要输入串行信号及控制信号,在 4096 位 LED 显

示屏上实现汉字或图案的实时显示,可以满足实际 工程应用的需要。

#### 参考文献

- 1 Panlnitkar S. Verilog—HDL 数字设计与综合. 夏宇闻,译. 北京: 电子工业出版社,2008

- 2 夏宇闻. Verilog 数字系统设计教程. 北京:北京航空航天大学出版社, 2008

- 3 常晓明,李媛媛. Verilog—HDL工程实践人门. 北京:北京航空 航天大学出版社,2005

- 4 周景润.基于 Quartus Ⅱ 的 FPGA/CPLD 的数字系统设计实例. 北京:电子工业出版社,2007

- 5 帅仁俊,张 齐. 基于 FPGA 的 LED 显示控制系统的设计和实现. 微计算机信息,2009;(26):133—135

# Design of LED Display Control System Based on FPGA

ZHANG Zhi-wei, ZHAO Feng

(School of Physics and Telecommunication Engineering, Shaanxi University of Technology, Hanzhong 723000, P. R. China)

[Abstract] LED industry is the most promising high-tech industry in the 21st century, according to the structural characteristics of the LED display module, combining with FPGA technology. It designed a large-screen LED display control system. Display control system consists of input interface modules, signal write control module, the signal read control module, read control module, memory module and dynamic control modules, using Verilog-HDL language for programming, the design achieved a series of processing of the external input signal, including the address generation, selection, storage and dynamic control. The experimental results show that: the system can realize the dynamic display of character or pattern, has a practical application.

[Key words] FPGA LED control system Verilog design