全球示波器市场的领先供应商泰克公司日前宣布,推出业内首款针对下一代移动内存技术——JEDEC LPDDR4的完整物理层及一致性测试解决方案。将于2015年开始采用的LPDDR4技术基于目前的LPDDR3技术,其数据速率将增加到4.26 Gb/s,并使用超低电压核心使功耗降低约35%,以提高智能手机、可穿戴设备和平板电脑等移动设备的性能。

由于仅有1.1V的低输入/输出电压、高数据速率以及使得测试非常不方便的紧凑机械设计,LPDDR4带来了新的测试和测量挑战。另外,参考电压 (Vref)、读突发 (read burst) 和写突发 (write burst) 方面的许多变化也使得进行JESD209-4规范所要求的测试变得更加复杂。泰克为设计工程师测试其LPDDR4设计提供最完善的工具集。通过自动化的设置及测试执行,泰克解决方案能够将其测试周期从之前的1个星期或更长时间缩短到1小时。

“LPDDR4无疑显著增加了(内存)确认对整个移动内存生态系统的复杂性和挑战,无论是对硅芯片供应商还是系统集成商都是如此”,泰克公司高性能示波器总经理Brian Reich表示,“为了高效地将这一令人激动的新技术推向市场,我们提供涵盖整个内存验证范畴的必要测试和测量工具——从高性能示波器和探头到先进分析软件。”

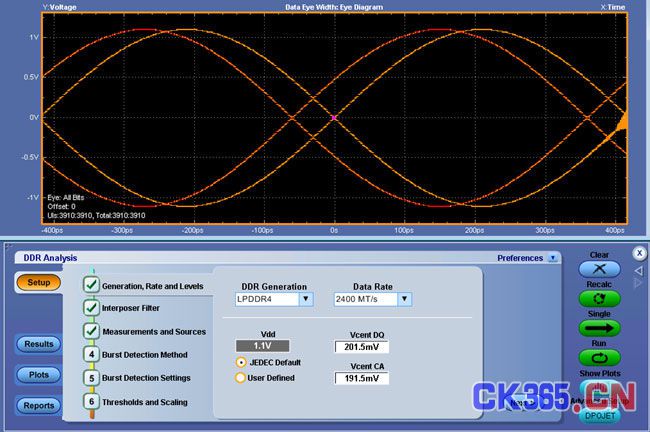

通过此次发布,泰克的DDR-LP4分析软件现在提供针对LPDDR4新标准的综合性物理层测试和调试。通过自动化测试设置和执行,DDR-LP4使内存设计工程师自信其设计能够完全符合内存标准。如果内存系统在一致性测试中失败,设计工程师能够快速切换到调试模式,并使用泰克示波器的强大Visual Trigger(可视触发)功能等工具来隔离相关事件,以便利用DPOJET抖动和眼图测量工具集进行更深入的根本原因分析。

LPDDR4插补器

泰克还与合作伙伴Nexus Technology联合推出业内首款具有两项插补器设计专利的LPDDR4内存器件插补器。EdgeProbe插补器是为满足移动设计的严格机械要求而设计的,而带插座插补器具有使用简便、可重复使用和器件可互换的特点。