摘要:介绍了CCD驱动电路的4种常用方式及其优缺点,详细阐述了基于高速超微型单片机C8051F3(x)的CCD驱动电路设计,包括内部CCD驱动时序和外部输出同步信号的产生、像素输出电压的简单处理以及通过RS232接口在线调整CCD驱动频率等。系统克服了目前单片机方式在CCD驱动应用中存在的一些缺点。

关键词:C805lF300 CCD TCDl206可编程计数器阵列

CCD作为一种光电转换器件,由于其具有精度高、分辨率好、性能稳定等特点,目前广泛应用于图像传感和非接触式测量领域。在CCD应用技术中,最关键的两个问题是CCD驱动时序的产生和CCD输出信号的处理。对于CCD输出信号,可以根据CCD像素频率和输出信号幅值来选择合适的片外或片内模数转换器;而对于CCD驱动时序,则有几类常用的产生方法。

1 常用的CCD驱动时序产生方法

CCD厂家众多,型号各异,其驱动时序的产生方法也多种多样,一般有以下4种:

(1)数字电路驱动方法

这种方法是利用数字门电路及时序电路直接构建驱动时序电路,其核心是一个时钟发生器和几路时钟分频器,各分频器对同一时钟进行分频以产生所需的各路脉冲。该方法的特点是可以获得稳定的高速驱动脉冲,但逻辑设计和调试比较复杂,所用集成芯片较多,无法在线调整驱动频率。

(2)EPROM驱动方法

这种驱动电路一般在EPROM中事先存放所有的CCD时序信号数据,并由计数电路产生EPROM的地址使之输出相应的驱动时序。该方法结构相对简单、运行可靠,但仍需地址产生硬件电路,所需EPR0M容量较大,同样也无法在线调整驱动频率。

(3)微处理器驱动方法

这种方法利用单片机或DSP通过程序直接在I/O口上输出所需的各路驱动脉冲,硬件简单、调试方便、可在线调整驱动频率。但由于是依靠程序来产生时序,如果程序设计不合理,会造成时序不均匀;而且往往会造成微处理器资源浪费;通常驱动频率不高,除非采用高速微处理器。

(4)可编程逻辑器件驱动方法

这种设计方法就是利用CPLD、FPGA等可编程逻辑器件来产生时序驱动信号,硬件简单、调试方便、可靠性好,而且可以得到较高的驱动频率。同样也可在线调整驱动频率。电路设计完成以后,如果想更改驱动时序,只需将器件内部逻辑重新编程即可。

以上4类方法中目前常用的是微处理器驱动方法(通常又称为“软件驱动”法)和可编程逻辑器件驱动方法(又称“硬件驱动”法)。由于在CCD应用系统中,一般都要用到微处理器,所以若采用“软件驱动”法,则无需增加硬件,在电路结构上最为简单,系统成本也最低,因此,只要能克服其驱动频率低、资源浪费多、时序不均匀等缺点,无疑是一种理想的驱动方法。本文结合Toshiba公司的TCDl206线阵CCD,介绍如何利用C8051F300来产生其要求的驱动时序。

2 硬件设计

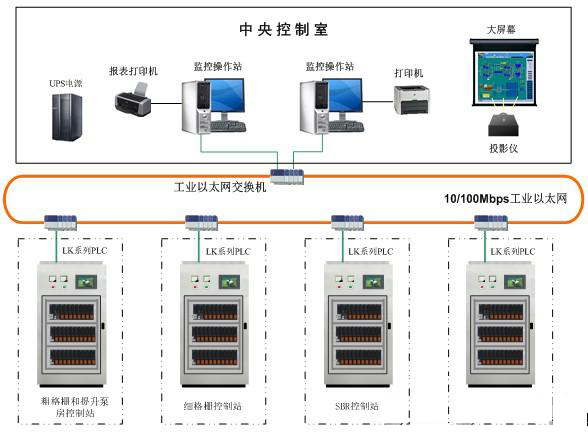

如图1所示,虚线框内的电路构成CCD驱动处理板。安装在CCD相机内部。系统处理器采用美国Silabs公司推出的超微型高速8位单片机C8051F300,CCD采用Toshiba公司的高灵敏度线阵CCD图像传感器芯片TCDl206,双电压供电的总线驱动器LVC4245解决了单片机(3.3V)和CCD(5V)二者之间的电平匹配。CCD驱动脉冲由C8051F300提供,其像素输出电压经高速运放AD8031处理,由U0引脚引到外部,同时向外部提供像素同步信号PS和行同步信号FS(由PO.6、P0.7经LVT245总线驱动器所得)。

U0、PS、FS这3个信号供外部处理器采集CCD像元输出。另外,有时可能要在线调整CCD的某些参数(如驱动频率、积分时间等),为此设置了RS232串口与外部处理器进行通信。

2.1 TCD1206

TCD1206是Toshiba公司生产的高灵敏度二相双沟道线阵CCD图像传感器芯片,2160个有效像素点,像素频率为0_3~2MHz(本系统为1.MHz),其驱动时序波形如图2所示。

图2中:φl、φ2为像素脉冲,两者互为反相,RS为复位脉冲.SH为光积分脉冲,OS为像元输出,DOS为像元补偿输出。当SH为低电平时,在φ1、φ2交变后,OS输出像元电压信号,随后发RS脉冲,以便去掉信号输出缓冲中的残余电荷,为下一点像素电压输出做准备。各脉冲具体时序关系可参见参考文献。

2.2 C8051F300

C8051F系列单片机其CPU内核采用流水线结构,机器周期由标准8051的12个系统时钟周期降为1个系统时钟周期,使其执行速度在相同晶振下是标准8051的12倍,处理能力大大提高,大部分C8051F单片机的峰值处理速度是25M1PS,而C8051F12X、13X系列的峰值处理速度则达到了100MIPS。C8051F系列单片机功能齐全,性能优异,其整体性能超过很多目前的16位单片机,甚至在一些低端应用中可取代低速的16位DSP器件,目前在仪器仪表、工业控制、嵌入式产品等领域日益得到广泛应用。

C8051F300是C8051F系列中的超微型高速混合系统级单片机,是目前世界上最小封装的8位单片机,11个引脚,封装在面积为3ram×3mm的芯片上。内部集成了3个16位定时器、3个可编程捕捉,比较模块、1个UART串口、1个I2C串口、1个8通道500KSPS采样率的8位ADC、8KB的Flash程序存储器、256B的内部RAM、8个I/O口,系统内部振荡时钟为24.5MHz(±2%)、最大峰值处理速度可达25MIPS。

由图2可见,在4路CCD驱动脉冲中,对时序要求严格的是φ1、φ2和RS,为此,利用C8051F300的可编程计数器阵列模块的2个可编程捕捉,比较模块输出口(CEXO、CEXl)自动产生φl、φ2,以CEXO为基准点,再产生RS和其他脉冲。

2.3 可编程计数器阵列(PCA)

PCA提供增强的定时器功能,由一个专用的16位计数器,定时器和3个16位捕捉,比较模块组成,每个捕捉/比较模块有其自己的I/O口(CEXn,n=l,2,3)。计数器,定时器的时基信号可在6个时钟源中选择:系统时钟、系统时钟/4、系统时钟/12、外部振荡器时钟/8、定时器0溢出或ECI输入引脚上的外部时钟信号。而每个捕捉,比较模块都可以被独立配置为6种工作方式之一:边沿触发捕捉、软件定时器、高速输出、频率输出、8位PWM和16位PWM。

由于φ1、φ2(对应CEXO、CEXl)是占空比为50%的方波,所以捕捉/比较模块0、1工作在频率输出方式,这种工作方式可在CEXn引脚产生可编程频率的方波,其工作原理图如图3所示。当PCA计数器低字节与捕捉,比较寄存器低字节相同即PCAOL=PCAOCPLn时,称为“比较匹配”,此时CEXn引脚电平翻转,同时捕捉/比较寄存器高字节即PCAOL与PCAOCPHn相加后的结果送入PCAOCPLn,以便下一次比较用。显然,只要改变PCAOCPHn的值,便可在CEXn引脚上得到频率可调、占空比为50%的方渡,其频率由下式定义:

fCEXn=fPCA/(2×PCAOCPHn),

其中:fPCA是PCA计数器,定时器的时钟频率。

3 软件设计

为了得到时序严格的ccD驱动脉冲和外部输出同步脉冲,程序不是靠软件延时来达到合适宽度的脉冲,而是利用PCA模块本身强大的功能,用中断程序来完成各路脉冲,即开放捕捉,比较模块0的“比较匹配”中断作为同步信号,并以此为基准点完成相应脉冲的每一次变化。

3.1 CCD驱动脉冲

PCA的2个捕捉,比较模块工作方式设置为如图4所示的频率输出方式。其输出引脚CEX0、CEXl的初始电平设置为1、0,当PCAOL与PCAOCPLn(n=O、1)“比较匹配”时,电平翻转,由此形成反相的φ1、φ2脉冲;而HS脉冲的产生,则是在捕捉/比较模块O的“比较匹配”中断程序中,即先对RS(P0.2)置l,随后清零,这样就可产生80ns的RS脉冲(SETB bit指令周期为2个时钟周期,即80ns)。

3.2 外部输出同步脉冲及像素电压

行同步信号FS、像素同步信号IX5均设置为低电平有效,CCD时序中φl、φ2交变后直到像素电压输出有一个延迟时间tdly(典型值为150ns),但由于捕捉/比较模块0“比较匹配”时,一方面CEXO(φ1)翻转,一方面向CPU请求中断,而中断响应时间需5个时钟周期(200ns),显然大于tdly,所以进入中断后,不必考虑tdly,可直接对PS(P0.6)清零,待合适的时间后再将PS置1.这样就产生一个低电平有效的PS信号。

CCD像素输出OS、DOS经高速运放AD8031处理后,其外部输出像素电压Uo时序如图4所示。

针对单片机在CCD时序驱动应用中存在的优缺点.选用新型高速C8051F单片机,实现CCD驱动电路,克服了单片机驱动方式存在的驱动频率低、系统资源浪费、时序间隔不均匀等缺点;具有硬件结构简单、调试编程方便、可在线调整驱动频率等优点。本文所介绍的驱动电路己应用于TCDl206,超微型的封装结构使其很容易与其他芯片一起嵌入在CCD相机中,系统运行可靠。