数字X射线(DXR)系统以固态传感器代替胶片式探测器,包括平板探测器和线性扫描探测器。平板探测器采用直接或间接变频。在直接变频中,硒光电池组成电容性元件,直接将高频光子转换为电流信号。

而在间接转换中,碘化铯闪烁计数器首先将光子转换为可见光,然后硅光电二极管阵列将可见光转换为电流信号。每个光电二极管代表一个像素。低噪声模拟前端将来自每个像素的小电流转换为大电压,然后再将电压转换为数字数据并传递给图像处理器。

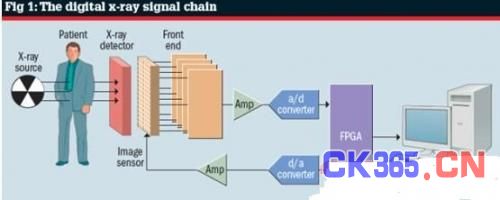

典型的DXR系统(见图1)能以高采样速率将多个通道多路复用至单ADC,同时不会牺牲精度。

图1:数字X射线信号链

DXR检测器的制造商通常使用间接转换系统,在此类系统中,一百万像素以上的平板探测器或光电二极管阵列捕获光子能量,将输出多路复用至12个或24个ADC.这项技术具有高效的X射线光子吸收和高信噪比,以一半的X射线照射量实时获得动态高分辨率图像。每像素的采样速率较低,数值从针对骨头和牙齿的几Hz,到获取婴儿心脏图像所需的最高120Hz.

医疗成像系统必须提供质量更佳的图像,以实现精确诊断和更短的扫描时间,降低病人所受X射线的照射量。

高性能数据采集

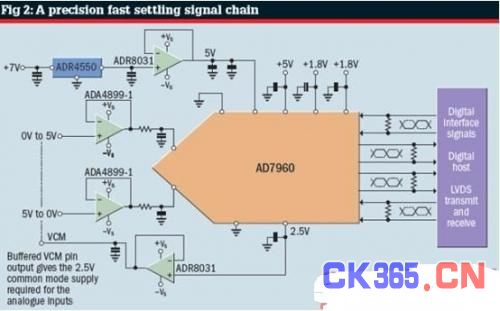

图2显示高精度、低噪声、18位数据采集信号链,提供±0.8 LSB积分非线性(INL)、±0.5 LSB差分非线性(DNL)以及99 dB信噪比(SNR)。

图2:高精度快速设置信号链

这类数据采集系统可用于CT、DXR以及其他医疗成像应用中,这些应用都要求在不牺牲精度的前提下提供更高的采样速率。该系统的18位线性度和低噪声性能可提升图像质量,而其5 MSPS的吞吐速率可缩短扫描周期、降低暴露在X射线下的剂量。

对多个通道进行多路复用处理可获得分辨率更高的图像,用于器官(如心脏)的完整分析,实现成本合理的诊断,并最大程度降低功耗。精度、成本、功耗、尺寸、复杂性以及可靠性等极为重要。

在CT扫描仪中,每通道使用一个采样保持电路捕获连续像素电流,并将输出多路复用至高速ADC.高吞吐速率允许将很多像素多路复用至单个ADC,可节省成本、空间与功耗。低噪声和良好的线性度提供高质量的图像。高分辨率红外摄像机可从该分辨率中获益。

过采样是以比奈奎斯特频率高得多的速率来对输入信号进行采样的过程。过采样用于光谱分析、MRI、气相色谱分析、血液分析以及其他需要具有宽动态范围的医疗仪器中,以便精确监控并测量多通道的小信号与大信号。高分辨率和高精度、低噪声、快速刷新速率以及极低的输出漂移等性能可大幅简化MRI系统的设计,降低开发成本与风险。

MRI系统的关键要求之一是在医院或医生办公室中可重复、长期稳定地测量。

为了获得更佳的图片质量,这些系统还要求具有更高等级的线性度以及高动态范围,范围从直流到几十kHz.原则上讲,对ADC进行4倍过采样可额外提供1位分辨率,或增加6 dB的DR.由过采样而获得的DR改善为:DR = log2 (OSR) x 3dB.许多情况下,Σ-Δ型ADC可以很好地实现过采样,但要求在通道间实现快速切换或要求进行精确直流测量时,过采样会受到限制。采用逐次逼近型转换器进行过采样还可改善抗混叠性能,降低噪声。

转换器架构

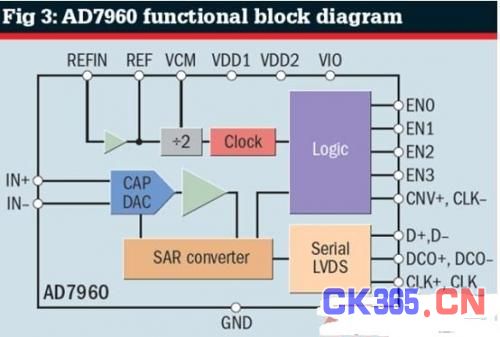

成像系统和过采样应用中使用的精密高速数据采集系统需要先进的ADC.18位、5 MSPS PulSAR差分ADC AD7960(见图3)采用容性DAC提供无延迟或流水线延迟的噪声和线性度。该器件具有宽带宽、高精度(100dB DR)以及快速采样(200ns)性能,可用于医疗成像应用,同时极大降低了多通道应用的功耗和成本。

图3:AD7960功能框图

容性DAC由差分18位二进制加权电容阵列(该阵列还可作为采样电容使用,采集模拟输入信号)、比较器以及控制逻辑组成。采样阶段结束后,转换控制输入(CNV±)变为高电平,输入IN+和IN?之间的差分电压被捕获,转换阶段开始。

电容阵列中的每一个元件在GND和REF之间逐次切换,电荷被重新分配,输入与DAC值进行比较,且位根据结果予以保留或丢弃。该过程结束时,控制逻辑产生ADC输出代码。AD7960将于开始转换后约100 ns时返回采样模式。采样时间约为总周期的50%,这使AD7960易于驱动,同时放宽了ADC驱动器的建立时间要求。

AD7960系列采用1.8 V和5 V电源供电,以自时钟模式转换时的功耗为39 mW (5 MSPS)。AD7960提供3种外部基准电压选项:2.048 V、4.096 V和5 V,同时片内缓冲器使2.048 V基准电压翻倍,因此转换等效于4.096 V或5 V.

数字接口采用LVDS,具有自时钟模式和回波时钟模式,提供转换器和主机处理器之间的数据传输(最高达300 MHz)。由于多个器件可共享时钟,因此LVDS接口降低了数字信号的数量,简化了信号路由。

它还能降低功耗,这在多路复用应用中尤为有用。自时钟模式利用主机处理器简化接口,允许接头采用简单时序同步每次转换的数据。若要让数字主机采集数据输出,则需要用到接头,因为数据不存在时钟输出同步。回波时钟模式提供稳定的时序,但要使用一对额外的差分对。

ADC驱动器

转换器的采集时间决定了ADC驱动器的建立时间要求。运算放大器的数据手册通常提供线性建立时间与压摆时间相结合的建立时间规格;本文提供的公式为一阶近似,假设线性建立和压摆均为50%,采用5 V单端输入。

AD8031轨到轨放大器缓冲ADR4550基准电压的5 V输出。第二个AD8031缓冲ADC的2.5 V共模输出电压。其低输出阻抗可保持稳定的基准电压,与ADC输入电压无关,从而最大程度降低INL.AD8031具有大容性负载稳定性,可驱动去耦电容,以便最大程度降低瞬态电流引起的尖峰,是各类低功耗应用的理想之选。