1)因为FPGA具有开发周期短,可更新等优点,现在有越来越多的通讯系统采用FPGA作为实际产品方案。已经有大量的FPGA应用到通讯系统中,为了降低系统维护的人力成本,需要能够实现FPGA远程版本更新。本文将以Xilinx Virtex6为例描述如何实现远程FPGA版本更新/重启。

2)FPGA加载主要分为2大类,一类是主动模式(master)另一类是从模式(slave)。在主动模式时FPGA会外挂存储器存储FPGA bit映像,FPGA会主动提供时钟访问外部存储器。在从模式时,FPGA作为从设备被挂在控制器CPU上由处理器控制对FPGA编程。上述两种模式中,因为从模式FPGA由外部CPU控制编程,可以通过远程更新CPU文件就可以实现对FPGA的版本更新,非常方便。但是当CPU外挂的FPGA较多时会使系统加载时间过长,降低系统启动速度。这里将利用FPGA多重启(multi-boot)功能实现在主动模式下版本更新。

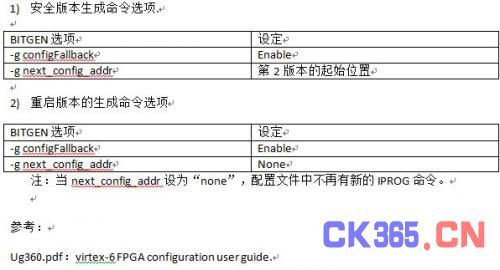

3)远程更新流程

当系统需要升级时,中心控制系统需要将新的FPGA比特映像文件直接发布到远程子系统,由远程子系统将比特文件更新到非易失存储器。然后由FPGA内部控制逻辑重新启动。比特映像文件更新后,下次上电启动将从新的比特映像文件。

图1. FPGA远程更新系统

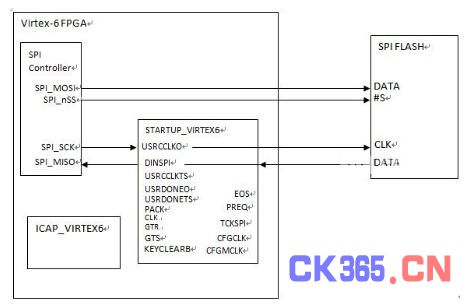

多重启动FPGA介绍

a)多重启动介绍

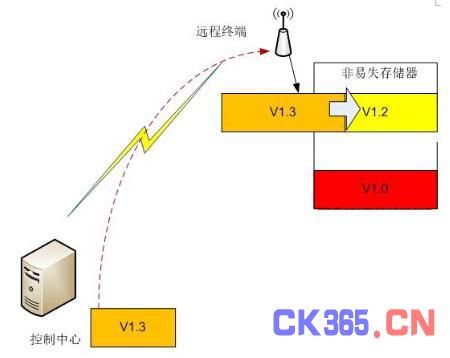

VIRTEX6可以支持2套配置文件,第一个版本为安全版本存放在起始位置(spi起始地址为0),第二个版本为最终启动版本。当FPGA启动时,加载控制器会从地址0开始读取加载指令。当读到WBSTAR和IPROG指令时,控制器就跳转到WBSTAR指定的地址读取新的加载指令。在第二个配置文件中不再发IPROG指令,控制其将顺序执行以直到配置文件结束。配置顺序如图2.

图2 对配置文件加载过程

b)多重启动模块

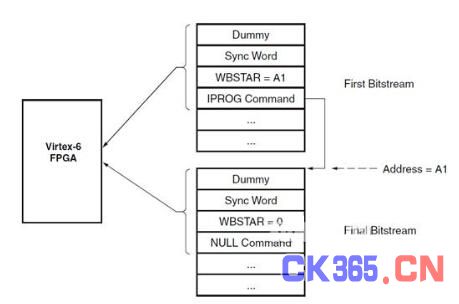

i)配置存储器访问接口

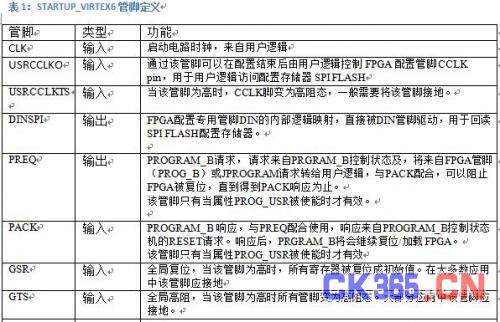

在FPGA配置过程中,FPGA通过指定的配置管脚访问外部非易失存储器,当配置结束后,部分管脚被释放可以用作普通逻辑管脚,但部分FPGA配置管脚是配置专用,在用户应用中是不可见的,需要例化专用模块STARTUP_VIRTEX6才能允许用户逻辑访问这些专用管脚。

图3 VIRTEX6访问外部存储器逻辑框图

ii)FPGA重启模块ICAP

ICAP_VIRTEX6为用户逻辑提供FPGA加载功能,它的功能与普通上点加载用的SELECTMAP加载功能相同。接口信号见表表2:ICAP_VIRTEX6接口信号

通过ICAP_VIRTEX6,用户逻辑可以发指令让FPGA从指定的位置重新加载配置文件。加载指令的发送顺序为,

1.发同步字

2.将要加载文件的起始地址写道WBSTAR寄存器(Warm Boot Start Address Register)

3.发送IPROG指令

4.FPGA从WBSTAR寄存器指定地址开始读取配置数据。

下面是一个控制ICAP从地址80000重加载例子

4)远程更新的可靠性

在远程更新过程中有多种原因可以造成远端的配置文件出错。比如数据传输错误,所以在跟新完成之后需要回读校验。为了减少传输负载可以采用CRC校验。但是如果在版本更新过程中出现掉电或系统重启,由于非易失存储器中的配置影像文件已经被破坏,远程终端将无法启动。为了避免这种情况的发生,远程终端需要有2套配置文件,当一套配置文件出错时,系统可以回退到备份配置文件启动。这样就可以保证当系统出错时,远程终端仍可以启动,接受控制中心发出的版本更新指令重新进行更新。

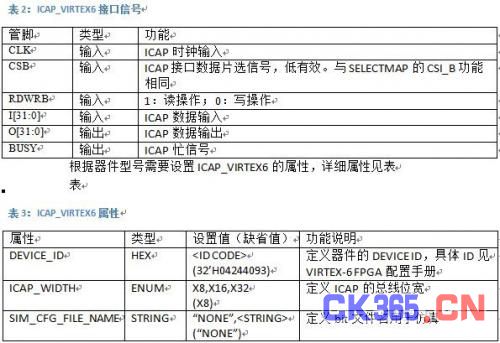

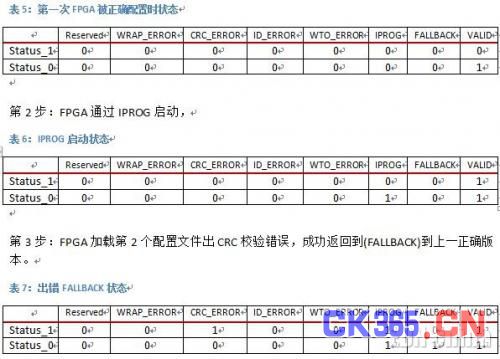

内部发重启过程和状态

第1步:第一次FPGA被正确配置,状态如下

在FALLBACK时,配置文件中的IPROG命令不再起作用。