引言

当今的嵌入式系统开发人员面临前所未有的挑战,努力向市场推出最具竞争力的产品。

直到最近,实现的大部分系统还局限于需要大量软件而且功耗非常高的多芯片系统或者昂贵的SoC ASIC.但是,越来越多的设计团队感到受市场压力以及资源限制的影响,这些方法的吸引力越来越低。而对于基于ARM 的嵌入式系统,FPGA 技术、知识产权(IP) 以及设计工具的发展促进了用户可定制SoC FPGA 的诞生。这些器件不但克服了传统方法的缺点,而且在嵌入式系统实现上非常独特,具有明显的优势。

应用广泛的ARM 处理器

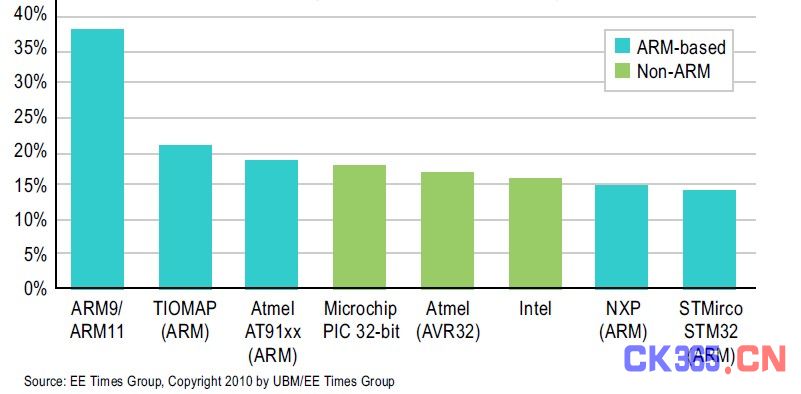

仅仅几年前,处理器市场还是四分五裂。PowerPC、RISC、MIPS、SPARC 以及很多其他平台都在竞争市场主导地位。但是,随着市场的成熟,而且越来越专业化,某些平台在一些应用领域中脱颖而出。特别是嵌入式系统应用领域的ARM 处理器( 图1) 尤其如此。

图1. 嵌入式系统应用中流行的平台

在发展迅速的嵌入式系统市场上应用非常广泛的ARM 处理器非常适合设计人员使用。

首先,发展非常成熟的软件、开发工具和ARM 兼容器件辅助系统实现了能够协同工作的解决方案工具箱。其次,受迅速发展的ARM 市场规模经济因素的影响,出现了更好、更先进的系统实现选择。

嵌入式系统设计挑战

与以往相比,嵌入式系统开发人员必须建立高性价比系统。迅速扩张的全球市场对设计人员的要求越来越高。但中国、印度和拉丁美洲等新兴市场领域的机遇也越来越多,这些市场越来越重要,不容忽视。为满足越来越高的用户基本需求,需要支持各种标准和价格、性能以及特性的平台。而且,竞争在全球展开,这对设计团队的压力更大,要求在越来越小的市场窗口内推出特性丰富的产品。

然而,对嵌入式产品的要求如此之高,设计团队却在不断减少。经济压力迫使很多公司缩减规模,设计资源也由此受到影响。结果,开发团队的规模在缩减,而工作强度却在增大。

对成本非常关注的基于ARM 的嵌入式系统设计人员越来越明显的感受到这一压力,清楚的认识到传统实现方法的缺点。多芯片解决方案实现起来相对容易一些,但是成本高,缺乏灵活性,性能/ 功耗指标达不到目前应用的需求。采用了软核处理器的单芯片解决方案实现起来也相对容易一些,但是难以达到功耗和性能目标。ASIC SoC 具有板上硬核ARM 内核,功耗和性能表现非常出色,但是面市时间长,不灵活,对于大部分应用而言成本过高。为提高竞争力,嵌入式系统开发人员需要一种能够帮助他们开发独具优势产品的解决方案,非常灵活,效率也非常高。

新一类SoC

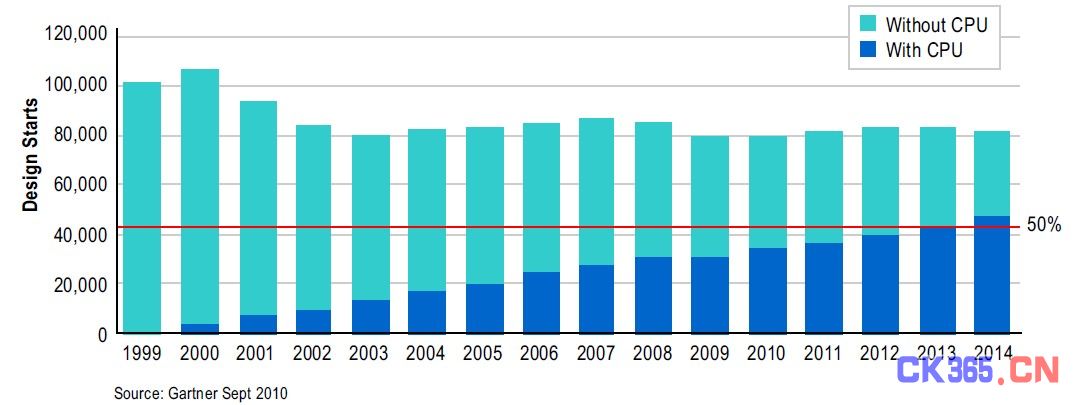

在过去十年中,FPGA 内置嵌入式处理器的应用在稳步增长( 图2)。由于Altera 在FPGA 技术上的进步,出现了新一类SoC 器件,满足了目前嵌入式系统应用的多种功能需求。基于ARM 的SOC FPGA 在一个SoC 中结合了硬核ARM 处理器、存储器控制器以及外设和可定制FPGA 架构。这些SoC FPGA 解决了设计人员面临的很多难题,突出了产品优势,价格和性能达到最优,产品能够及时面市,延长了产品使用寿命。

图2.FPGA 中处理器的发展

SoC FPGA

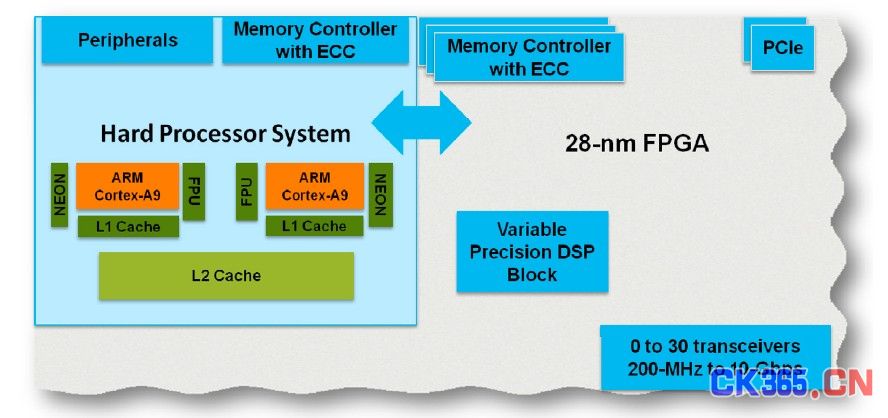

基于ARM 的SoC FPGA ( 图3 所示) 在单片FPGA 中紧密结合了经过优化的“硬核”处理器系统(HPS) 模块。HPS 包括双核ARM 处理器、多端口存储器控制器以及多个外设单元,处理器性能达到4,000 DMIPS (DhrySTONes 2.1 基准测试),功耗不到1.8 W.这些硬核IP 模块提高了性能同时降低了功耗和成本,减少了对逻辑资源的占用,突出了产品优势。用户可以定制片内FPGA 架构,开发专用逻辑。可编程功能支持采用新的或者修改后的通信标准和网络协议,进一步调整性能。

图3. 处理器与FPGA 架构紧密集成

与传统的解决方案相比,SoC FPGA 在性能上有明显的优势。硬核单元相对于软核IP 进行了很大的优化,在所采用的工艺节点上,实现了最好的性能、最低的功耗以及最高的密度。FPGA 通常是新工艺节点最先推出的器件,因此,设计人员利用SoC FPGA 能够使用最新最好的半导体技术。而且,与基于电路板的解决方案相比,片内总线紧密连接各个单元,进一步提高了性能和功效。从系统整体角度看,SoC FPGA 明显减小了系统体积,降低了功耗和成本。

产品更迅速面市

通过现场可编程平台,使用现成的器件开发定制基于ARM 的SoC FPGA,其开发时间和成本只是其他定制器件的一小部分。可靠的FPGA 设计工具、直观的系统集成工具以及成熟的ARM 辅助系统相结合,加速了开发过程,降低了风险。即使是第一次实现FPGA的设计人员,目前常用的工具支持接口格式和标准,因此,他们可以比较轻松的重新使用已有软件、IP 和其他设计内容。使用SoC FPGA 平台,利用开发基础支撑条件,开发人员能够很快抓住嵌入式系统市场的机遇。

灵活性

在嵌入式系统市场上应对竞争需要很高的灵活性。网络和通信应用必须适应新的或者变化的标准。工业和医疗供应商不一定需要大批量产品,但是对专业化产品有很大的需求。不考虑特殊应用领域,嵌入式系统开发人员必须能够灵活的应对激烈的竞争,利用最新的技术,很快抓住新的市场机遇。

SoC FPGA 非常适合满足嵌入式市场需求。基于ARM 的SoC FPGA 中的逻辑部分很容易应对各种变动,适用性较强。在SoC FPGA 中,逻辑是现场可编程的,意味着很容易迅速修改,以突出产品优势,进行更新或者重制某一产品型号。在有保证的情况下,即使设备在现场部署后,也可以进行重新配置。

可更新和设计重用

设计重用是管理成本、缩短市场窗口、提高设计资源利用率的关键手段。能够在多个器件和系列中调整并重新使用设计内容,这种能力是无价的。当把现有设计或者IP 模块应用到体积、功耗和性能需求都不同的器件上时,借助这种方法,设计人员不需要从头开始重新进行设计。由于越来越多的设计团队分散在世界各地,重新使用功能不但提升了效能,而且提供了共享和利用已有内容的好方法。

SoC FPGA 体系结构支持多个IP 内核,灵活的适应不同的器件系列。很多应用都有不同的价格、性能、功耗和其他限制,采用可重用和可更新内容很容易满足这些需求。随着工艺技术的进步,采用这类FPGA 系列,通过在下一代产品中导入IP,能够方便的移植到下一工艺节点。

长寿命产品

对于很多应用而言,长寿命产品是要考虑的重要因素。产品生命周期,特别是医疗、工业和军用器件,长达10 到15 年,甚至更长。但是,IC 供应商的产品一般只供应较短的时间。当这类产品的产品生命周期超过其IC 组件时,设计人员会有很大的成本代价,花费宝贵的设计资源进行设计移植,或者重制。

为避免产品过时或者失效问题的不利影响,建议需要较长产品生命周期的嵌入式系统开发人员选择经过严格可靠性测试的实施方案,供应商在预期的产品生命周期内都能够提供支持。由于其长寿命并且容易移植,工业、军事、航空航天、汽车以及医疗应用一直在采用FPGA.长寿命器件意味着很少在现场进行产品维护,从而降低了维护成本,支持将设计资源应用到新产品上。

Altera SoC FPGA

作为2011 年启动的“嵌入式计划”的一部分,ALTEra 为嵌入式系统市场提供28-nm基于ARM 的SoC FPGA.这些Altera 产品具有:

■ 先进的硬核ARM 处理器、外设和高速互联。

■ 片内Altera FPGA 架构、第二个存储器控制器以及PCI Express (PCIe ) 接口。

■ 支持已有内容和IP 集成的设计工具。

■ 采用或者不采用硅片,加速软件开发的仿真环境。

硅片

在28-nm 工艺节点,Altera 使用了定制方法,在Arria ? V 和Cyclone ? V FPGA 系列中提供ARM 处理器,以满足多种嵌入式应用需求。在相同的TSMC 28-nm 低功耗(28LP)工艺上生产的两种系列产品都能够满足嵌入式系统的系统低功耗和低成本需求。

Altera 的Cyclone V FPGA 系列非常适合对功耗和体积要求较高的应用,而Arria VFPGA 系列在体系结构上为满足高性能嵌入式应用而量身定制。

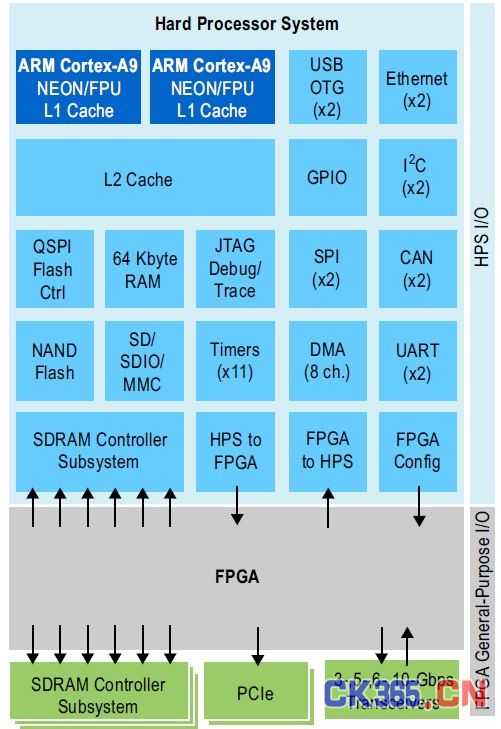

Altera ARM HPS ( 图4) 在全功能HPS 中结合了双核ARM Cortex ? -A9 MPCore ?处理器、存储器控制器以及外设IP.28-nm 工艺节点的高性能双核ARM Cortex-A9 MPCore 处理器工作速率高达800 MHz.双核配置实现了灵活的SoC FPGA 产品,其性能能够进一步满足未来的需求。内置NEON ?媒体处理引擎和双精度浮点单元为多媒体和信号处理应用提供了标准化加速功能。每个内核32 个32-KB Level-1 高速缓存,在512-KB 共享Level-2 高速缓存的支持下,通过减小延时和存储器访问时间,有助于提升性能。

图4. 基于ARM 的硬核处理器系统简介

除了ARM 内核本身,HPS 还包括SDRAM 控制器子系统、通用外设阵列,以及高速片内互联。外设组包括增强闪存控制器、MMC、DMA、USB 2.0、以太网、UART、SPI 和GPIO 接口。最后,Altera 独特的片内总线体系结构通过高速互联连接了HPS 和FPGA,总带宽大于125-Gbps.

在片内Altera FPGA 中实现了专用逻辑。由于能够长期稳定的为Cyclone V 和Arria VFPGA 系列提供支持,Altera 产品在正常工作条件下,使用寿命一般能够达到20 年以上。

快速系统设计工具

Altera 的Quartus ? II 开发软件提供了高效的设计环境,帮助开发人员迅速实现基于ARM 的SoC.所包含的Qsys 系统集成工具在IP 功能和子系统之间自动生成互联逻辑,从而显着缩短了设计时间,减轻了设计工作量。对于使用AMBA ?等通用接口标准和协议编写的IP,Qsys 自动识别IP,将其与SoC 连接。利用这一工具,很容易实现重用功能,在一片SoC FPGA 中同时使用已有或者第三方IP 单元以及不同的标准接口。此外,开发人员很容易利用现有的内容,迅速实现FPGA 开发。

软件开发

软件开发是开发嵌入式系统时非常重要的工作。出于这一原因,嵌入式软件开发人员一般使用名为“虚拟目标”的仿真环境,在能够使用硅片之前,编写、仿真并调试软件。利用Altera SoC FPGA 虚拟目标仿真环境,开发人员即使在拿到第一个硅片之前,也能够开始寄存器和二进制兼容软件开发。设计人员通过使用虚拟目标,提前完成大部分软件开发工作,降低了设计风险,更迅速的将产品推向市场。

结论

与以往相比,目前的嵌入式系统开发人员必须面对激烈的竞争,迅速应对多变的标准、协议和需求,以更少的资源满足越来越高的各种市场需求。含有硬核处理器内核的SoCFPGA 不但支持设计人员解决这些设计难题,而且还帮助他们获得了明显的产品及时面市、价格/ 性能、突出产品特点以及长寿命产品等优势。与传统方案相比,现在已经到达了一个关键点,基于FPGA 的SoC 成为可行而且是首选的方法,必将在市场上获得广泛应用。