1 基于FPGA的嵌入式系统开发流程

设计一个嵌入式系统,主要包括硬件平台搭建和应用软件编写。基于FPGA技术,硬件平台搭建和软件编写都可在相应的软件平台上完成。EDK(Embedded Development Kit)是Xilinx公司开发嵌入式系统的套件工具。EDK套件工具主要包括硬件平台产生器、软件平台产生器、仿真模型生成器和软件编译调试等工具,利用其集成开发环境XPS(platform studio)可以方便地完成嵌入式系统的开发设计[1],设计流程如图1所示。

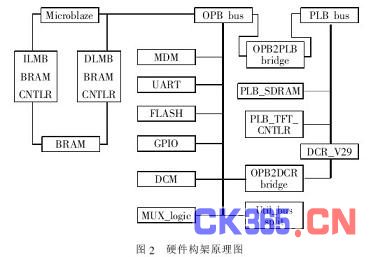

2 硬件平台搭建过程

分析系统需求中,铁轨检测主要是进行图像的分析处理,包括三个主要部分:图像输入、图像处理和结果显示。本项目使用依元素公司生产的Xilinx Spartan-3a系列xc3s700a的FPGA开发板,软件版本为Xilinx10.1。图像输入有下列途径:USB接口、RS232串口、100 M以太网接口、EDK套件XMD调试平台直接下载等。本文将图像数据转换为.ELF文件格式,直接烧写入Flash中。本文不追求实现视频流处理,并且图像要多次使用,源图像存储在Flash中最合理。图像处理由Microblaze软核系统和检测程序共同完成;图像显示由TFT控制器通过VGA输出信号在液晶显示屏显示。具体硬件平台搭建过程如下:

(1)按照XPS应用向导,建立最小系统,配置Microblaze软核系统参数和添加UART外设。

(2)添加IP核,并连接到相应总线,主要为内存控制器、通信控制和GPIO等。

(3)添加自定义的IP。尽管Xilinx提供了许多免费IP,但是免费的IP不能满足用户的所有设计。本项目需要自定义的IP有用于控制液晶显示的TFT_Controller和用于内存地址总线及数据总线复用的Mux_logic IP。PLB_TFT_Controller主要产生RGB信号、行场扫描、同步信号等,Mux_logic IP用于对SDRAM和Flash总线复用进行控制,输入为SDRAM和Flash的控制IP产生的地址总线信号和数据总线信号及使能信号,输出为复用地址总线、数据总线信号。

(4)配置相应IP,并进行信号互联,将需要控制硬件的port连接到外部。分配地址空间,添加UCF配置文件。

(5)生成硬件比特流文件和硬件驱动文件。硬件结构原理图如图2所示。

3 软件设计过程

3.1 铁轨检测原理

本项目中铁轨检测主要考虑两种方案[2]:基于边缘特征和基于区域特征。(1)基于边缘特征检测方法先在全局范围检测出边缘线,再通过模型或特征限制条件,从边缘图中获得目标边缘。(2)基于区域特征的铁轨检测,利用区域统计特性,即铁轨区域区别于周围环境独特统计特性来判断铁轨区域。两种方法中,前者检测到的铁轨线较为准确,但是其对二值化阈值严重依赖;后者抗噪性较好,但检测的铁轨线不够准确,本文主要讨论基于区域特征的铁轨检测。

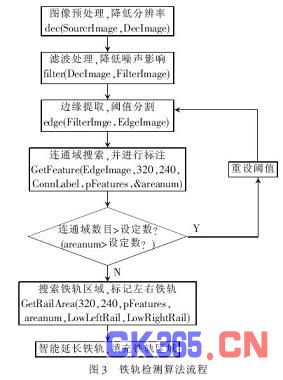

基于区域特征铁轨检测流程如图3所示,分为四个步骤:

(1)降低分辨率。在滤波之前,先降低图像分辨率,以消除图像细节,也可减轻后续处理的计算负担。

(2)滤波处理。分辨率降低后,图像中仍有很多的突兀点,这是因为铁轨上各种电磁信号的存在,摄像头采集到的图像不可避免地受到高斯噪声、系统噪声的污染。考虑到图像特征,选用中值滤波,它在平滑脉冲噪声方面非常有效,同时可以保护图像尖锐的边缘。

(3)边缘提取。利用边缘检测算子检查每个像素的邻域并对灰度变化率进行量化,包括方向的确定。Sobel边缘检测算子方向性灵活,可以设置不同的系数,抑制噪声效果较好,使用范围广泛,因此选用Sobel算子。同时铁轨图像横向变化不大,而在纵向有很大的延伸,故也只考虑图像垂直边缘响应。

(4)连通域搜索。二值化处理后边缘图包含了铁轨信息,也含有很多非铁轨边缘。使用八连通区域搜索法,进行标号处理,记录相互独立的连通区域个数并进行标号。对连通区域按照长度大小进行排列,直到搜索出纵向最长的两根铁轨,然后判断并标记左右两铁轨,之后进行区域填充,最终可以看到标记的铁轨区域。

3.2 OpenCV仿真结果

本项目程序首先实现OpenCV仿真,然后移植到FPGA中。OpenCV提供的图像处理算法非常丰富,并且部分程序以C语言编写,处理得当,不需要添加新的外部支持就可以完整的编译连接生成执行程序进行算法移植。本次仿真只运用“cv.h”和“highhui.h”两个OpenCV库,主要是运用其图像加载、图像显示等函数,而中值滤波、边缘检测、铁轨搜索函数自行编写。仿真结果如图4所示。

1 2

3.3 FPGA程序移植过程

3.3.1 图像输入与显示[3]

本项目把图像数据转换为.ELF文件格式,烧录到NOR-Flash,在XPS的菜单下点击Program Flash Memory,选择自动格式转换,即可进行烧录,而且可以指定烧录数据的位置。数据格式转换利用Matlab软件完成,程序如下:

由于是灰度图像,只读取其亮度值。图像分辨率为640×480。写数据可以用fprintf函数或fwrite函数,但是实验表明使用fprintf函数写数据,文件大小302 kB,显示图像不正常;而使用fwrite函数写数据文件仅300 kB,显示图像正常。说明两种函数写数据方式本质不同,造成写入数据格式不同。

图像显示过程:先从Flash中每次一行把数据读入BRAM,然后把每一位亮度值移位变为R、G、B三位,再从BRAM读数据到SDRAM显存,如此循环480次,用以显示图片。由于R、G、B值相同,显示的便是灰度图像。如果直接从Flash读数据到SDRAM显存,显示图像每行有不规则不连续的黑点,甚至显示不正常。显存的设置在TFT-Controller IP中完成,显存空间为2 MB,起始地址与SDRAM起始地址相同。

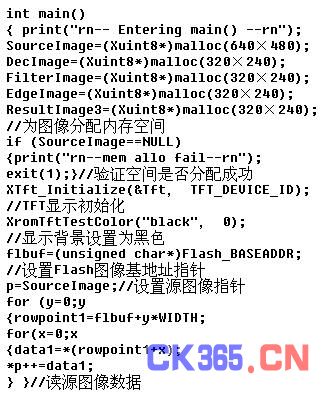

3.3.2 图像处理程序移植[3]

由于开发环境不同,移植后程序在独立系统上运行,需要对OpenCV仿真程序做一些改正。FPGA编程系统支持C语言标准库函数,所以打印输出显示函数print()、动态内存分配函数malloc()可以直接使用。尽管printf()函数也可以用于打印输出结果,但目的是把程序放入大小为32 KB的BRAM,实验表明它比print()函数占用空间大一倍。在OpenCV中,可以直接使用cvShowImage()、cvReleaseImage()、cvDestroyWindow()函数显示图像和释放内存空间,在移植程序中要自行设计这些函数。移植程序中subplot()函数用于在屏幕上显示4幅图像(降低分辨率源图像、滤波图像、阈值分割图像、铁轨检测图像),DeleteAllPointElems()函数用于释放内存空间。其他函数,例如降低分辨率函数Dec()、滤波函数filter()、边缘检测函数edge(),可以完全使用OpenCV中的程序,不需要做修改。移植后主程序如下:

FPGA图像处理结果如图5所示。

本文实现基于FPGA的铁轨检测算法,首先完成OpenCV程序仿真,然后移植到FPGA构建的硬件系统中,可以成功检测出铁轨所在区域,并在一定条件下进行铁轨智能延长。研究结果表明,检测一幅分辨率为640×480图像,大约需要30 s,如果应用于实时视频流系统中,则硬件平台设计需要进行精简,以提高速度。也可考虑基于硬核、多核技术,来提高处理速度,以满足实时视频流处理。